- Главная страница

- Карта сайта

- FAQ по «Байтам»

- Завод-изготовитель

- Статистика выпуска

- Внешний вид

- Комплектация

- Плата и комплектующие

- Клавиатура

- Источник питания

- Программное обеспечение компьютера «Байт»

- Описание портов компьютера «Байт»

- «Старый» вариант компьютера

- Встроенный в ПЗУ тест памяти

- ПЗУ с тестами памяти для ZX-Spectrum (и компьютера «Байт»)

- Эмуляторы компьютера «Байт»

- Видео по компьютеру «Байт»

- Восставшие из могилы (отчёты о ремонте некоторых «Байтов»)

- Общая информация

- Комплект поставки

- Процессорный модуль (клавиатура)

- Адаптер для подключения КВУ

- Контроллер внешних устройств (КВУ)

- Описание портов «Байт-01»

- Особенности программного обеспечения «Байт-01»

- Контроллеры дисковода (BDI)

- Дисководы

- Фотогалерея дисководов

- Электроника МС5305

- Электроника МС5311

- Электроника МС5313

- Электроника МС5350

- ЕС5325

- Дисководы Teac (общая информация)

- Teac FD-55F

- Teac FD-55FR

- Teac FD-55GFR

- Panasonic JU-475-3

- Panasonic JU-475-4

- Panasonic JU-475-5

- Mitsumi D509V2

- Mitsumi D509V3

- Mitsumi D509V5

- Epson SD-600

- Epson SD-680L

- Epson SD-700

- MF58D

- Canon MD5501A

- NEC FD1155C

- NEC FD1157C

- Джойстики для компьютера «Байт»

- Подключение к магнитофону

- Подключение HDD

- ROM-диск

- Плата тестового ПЗУ

- DivMMC

- Подключение к телевизорам и мониторам

- Расширение объёма ОЗУ

- Скачать всевозможную документацию и программы по теме сайта

- Скачать схемы и документацию по компьютеру «Байт»

- Скачать схемы и документацию по компьютеру «Байт-01»

- Spectrum-совместимые компьютеры

- Pentagon моей мечты (Pentagon-128)

- Pentagon-48

- Pentagon-1024

- Балтик

- Пик

- Ленинград-1

- Ленинград-2

- Интер (Квант)

- Этон

- Инфотон-030

- Ратон-9003 на дискретах

- Ратон-9003 на БМК

- SpeccyBob

- Астра

- Компаньон

- Компаньон-2

- Игровая приставка «Эльф»

- Описание

- Игры на оригинальных картриджах

- Любительские образы картриджей

- Доработки и апгрейд приставки

- Расширение памяти до 128К

- Информация по программированию приставки

- Реплики приставки (новодел)

- Оснастка для формовки выводов БМК

- Новодельный универсальный картридж

- Новодельный универсальный джойстик

- Процесс сборки образа картриджа

- Советские компьютеры

- DC/DC преобразователь напряжения для питания КР580ВМ80

- Периферия для ZX-Spectrum

- Магнитофоны и магнитолы «Беларусь»

- Электронные игры и приставки

- ОС iS-DOS и TASiS

- С чего всё началось

- Мусорка

- Ссылки по теме сайта

- Donate

- Обновления сайта

- Контакты

- Блог

- Справочник по некоторым специфическим микросхемам

- События

Spectrum-совместимые компьютеры «Байт»,«Байт-01» и прочие раритеты

8 / 414

Версия для печати

Расширение ОЗУ до 128К на компьютерах с одним полем ОЗУ

Расширение ОЗУ до 128К на компьютерах с раздельными полями ОЗУ

Принципы работы схем расширения ОЗУ

В этой статье я буду разбирать уже готовые схемы расширения ОЗУ для ZX-Spectrum. Всегда приятно посмотреть и понять как это делали умные люди. Ниженаписанная информация может быть сложна для понимания!

Сперва придётся немного углубиться в электронику, без этого мы не сможем понять как функционирует часть схемы Спектрума, ответственная за работу с ОЗУ.

ОЗУ в почти всех клонах ZX-Spectrum сделано на микросхемах динамической памяти. Почему так? Во-первых, в те годы, когда у нас производились Спектрумы, только микросхемы динамической памяти имели необходимый объём (16К*1, 64К*1 и даже 256К*1). В то время как микросхемы статического ОЗУ были ёмкостью хорошо если 8К*8. Во-вторых, микросхемы динамического ОЗУ были доступнее и дешевле. Поэтому Спектрумы (да и вообще все остальные компьютеры) делали только на динамических ОЗУ. Однако у микросхем динамического ОЗУ есть минусы - постоянная необходимость так называемой «регенерации» ОЗУ, чтобы микросхема «не забыла» записанную в ней информацию, а также ограниченное количество выводов (обычно 16), которое не позволяет напрямую адресовать нужный байт.

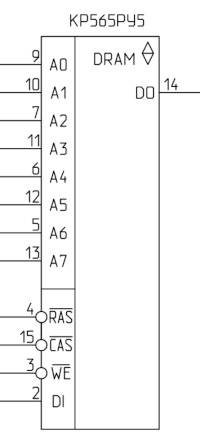

Возьмём для примера, пожалуй, самую распространённую для ZX-Spectrum микросхему ОЗУ КР565РУ5:

Микросхема сделана в 16-выводном корпусе. В то же время её объём составляет 65536 бит. То есть для задания адреса требуется 16 выводов (65536 - это 2 в степени 16). Итого, нам надо 16 выводов только для указания адреса, а у микросхемы всего 16 выводов... Не сходится? Чтобы вместить в 16 выводов микросхемы все нужные сигналы шина адреса сделана мультиплексированной. Адрес мы задаём в два этапа - сначала одну половину в 8 бит, потом вторую половину в 8 бит.

Кстати, это является ответом на вопрос, почему ёмкость динамических ОЗУ от модели к модели увеличивается в 4 раза (КР565РУ3/6 - 16К*1, КР565РУ5 - 64К*1, КР565РУ7 - 256К*1, 441000 - 1024К*1). Почему нет динамических ОЗУ объёмом 32К? А потому, что при переходе от РУ6 к РУ5 мы к адресной шине добавляем 1 бит, но за счёт мультиплексированной шины получаем увеличение в 2 бита, то есть в 4 раза (я тут не веду речь про экзотику типа КР565РУ5Д1 или Д2, которая по сути является браком ОЗУ КР565РУ5, и в которой рабочая только одна «половинка». В качестве примера можно взять «старый» вариант компьютера «Байт»).

Итак, для записи/чтения одного бита надо в два «захода» указать адрес. Не забываем про регенерацию - с определённой периодичностью (для КР565РУ5 - не реже, чем один раз в 2 мс) надо «перебрать» (то есть перечитать) адреса в ОЗУ, иначе микросхема начнёт «забывать» записанные данные. К счастью, перебирать надо не все адреса подряд, а только одну «половинку» адреса из 8 бит (то есть не реже, чем в 2 мс надо обратиться к ОЗУ 256 раз, указывая каждый раз новый столбец в матрице ячеек памяти). Итого имеем 3 варианта обращения к микросхеме: выбор первой «половины» адреса, выбор второй «половины» адреса и циклический перебор одной из половин адреса с определённой периодичностью.

Это была теория, теперь перейдём к практике.

ZX-Spectrum с общим полем ОЗУ

Под общим полем ОЗУ подразумевается, когда всё ОЗУ выполнено в виде одного массива микросхем, например для 64КБ ОЗУ используем одну «линейку» из 8 штук КР565РУ5.

В качестве компьютера с одним полем памяти, на примере которого я хочу описать работу схемы расширения ОЗУ до 128К, будет выступать «Ленинград-1» (как наиболее простой по устройству и пониманию принципа работы).

В качестве схемы расширения в этом разделе будут выступать платы расширения ОЗУ до 128К Б-1, С-1 и BC-1. Данные платы расширения ОЗУ работают по одному и тому же принципу и незначительно различаются в плане схемотехники. Таким образом с некоторыми допущениями можно сказать, что у них одинаковая схема. Эти платы рассчитаны на подключение к компьютерам «Балтик», «Пентагон-48», «Байт» и «Ленинград-1», схемотехнику и принципы работы последнего, как я уже говорил выше, буду брать за образец.

В «Ленинград-1 48К» все варианты обращения к ОЗУ можно представить в виде таблицы:

| /RAS=1 | /RAS=0 | ||||||||||||||||

| MA0 (A0) | MA1 (A1) | MA2 (A2) | MA3 (A3) | MA4 (A4) | MA5 (A5) | MA6 (A6) | MA7 (A7) | MA0 (A8) | MA1 (A9) | MA2 (A10) | MA3 (A11) | MA4 (A12) | MA5 (A13) | MA6 (A14) | MA7 (A15) | ||

|

H1=0

данные |

A0 | A1 | A2 | A3 | A4 | A5 | A6 | A7 | A8 | A9 | A10 | A11 | A12 | A13 | A14 | A15 | |

| H1=1 |

H2=0

пиксели |

H3 | H4 | H5 | H6 | H7 | V3 | V4 | V5 | V0 | V1 | V2 | V6 | V7 | 0 | 1 | 0 |

|

H2=1

атрибуты |

H3 | H4 | H5 | H6 | H7 | V3 | V4 | V5 | V6 | V7 | 0 | 1 | 1 | 0 | 1 | 0 | |

Но ничего не понятно, но очень интересно... Однако я всё объясню, пусть и предельно упрощённо.

В компьютере есть сигнал H1. Если он равен 0, значит идёт цикл обращения процессора к ОЗУ. При этом неважно хочет ли на самом деле процессор прочитать или записать данные в ОЗУ или нет. Просто при этом значении сигнала H1 процессору можно обращаться к ОЗУ. В другое время - никак нельзя :) По сигналу /RAS=1 в ОЗУ сначала фиксируется одна «половинка» адреса, затем при смене значения сигнала (/RAS=0) фиксируется «вторая» половинка адреса.

Если же H1=1, то процессор «отдыхает», и в работу включается видеоконтроллер, который занимается постоянным сканированием содержимого определённой области ОЗУ, выводя его на экран. Тут к нам добавляется ещё один сигнал - H2, по состоянию которого (совместно с H1=1) видеоконтроллер либо выводит на экран содержимое пикселей экрана (H2=0), либо выводит содержимое атрибутов (H2=1). Заодно при работе видеоконтроллера гарантированно перебираются 256 столбцов в каждой микросхеме ОЗУ (это делается при /RAS=1), осуществляя, таким образом, регенерацию данных.

С режимом чтения/записи данных процессором всё понятно - зафиксировали адрес, прочитали или записали данные. Обратите внимание, что процессору теоретически доступен весь объём ОЗУ - все 64КБ, включая область #0000-#3FFF, которую, как известно, занимает ПЗУ. Однако обращение к этой области ОЗУ «отсекается» в схеме компьютера, и вместо ОЗУ включается микросхема ПЗУ.

А вот с режимом вывода данных на экран дело обстоит несколько сложнее.

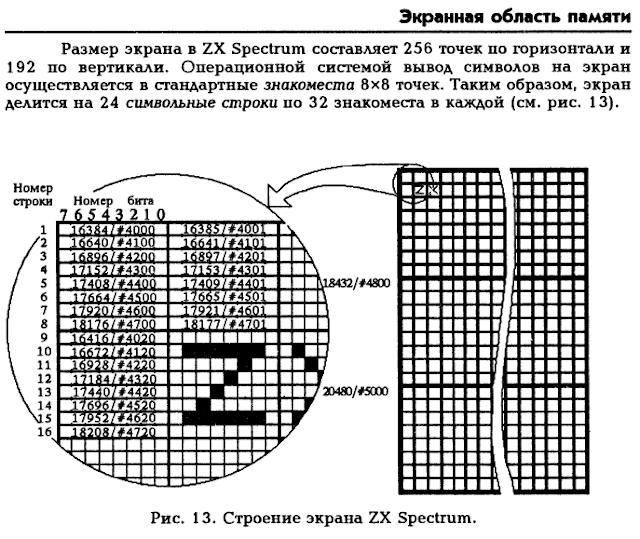

Как известно, экран в ZX-Spectrum состоит из 192 строк по 256 точек в каждой строке. При выводе изображения на экран последовательно сканируются строки начиная с верхней части экрана, и в каждой строке последовательно сканируются слева направо столбцы. Номера строк, которые выводятся в данный момент, задаются сигналами V0-V7. То есть в режиме вывода содержимого экрана сигналы V7-V0 меняются от %00000000 (0) до %00111111 (191), то есть перебираются 192 строки. Примерно то же самое происходит со столбцами. Только их число равно 32 (32 столбца по 8 бит дают 256 точек по горизонтали). Номера столбцов задаются сигналами H3-H7.

Столбцы сканируются линейно, это видно из таблицы - номера столбцов идут последовательно от H3 до H7. Однако почему такое не происходит со строками? У них какая-то странная нумерация, а для части адресов вообще заданы значения 0 и 1...

Всё дело в организации экранной области ZX-Spectrum. Если вы помните, строки адресуются не линейно одна за одной, а сначала строка с номером 0, потом через 32 байта начинается строка с номером 7 и так далее...

Чтобы организовать вывод строк таким способом, биты V0-V7 «перепутаны» таким хитрым образом. Совместно с битами A15=0, A14=1, A13=0 сигналы V0-V7 образуют экранный адрес (#4000-#57FF).

Что же касается атрибутов (при сигнале H2=1), то битами A11-A15 задаётся адрес #5800, относительно которого последовательно перебираются 768 байт при помощи сигналов V3-V7 и H3-H7.

Расширение ОЗУ до 128К

Что же делать, если нам надо 128К RAM? Для начала, есть стандарт, согласно которому должна работать память 128К в ZX-Spectrum.

У нас сейчас (в 48К Спектруме) память распределяется следующим образом:

Весь объём доступной для адресации процессором памяти составляет 64 КБ и условно разбит на 4 области, именуемые CPU0-CPU3. Каждая область занимает по 16КБ. Так удобнее их адресовать - по двум битам шины адреса - A14 и A15. Область памяти CPU0 всегда (или почти всегда) занимает ПЗУ. Поэтому в схеме компьютера при обращении к памяти и комбинации битов A14=0 и A15=0 выбирается микросхема ПЗУ.

Область памяти CPU1 делят между собой процессор и видеоконтроллер. Если процессору нужно обратиться к этой области памяти, то в момент вывода изображения на экран процессор «подтормаживается» сигналом WAIT. Поэтому эта область памяти называется «медленная».

Далее идут подряд две области памяти CPU2 и CPU3.

В случае увеличения объёма ОЗУ мы не можем физически расширить адресуемую процессором память - больше чем 64КБ памяти он не сможет адресовать. Поэтому используется «оконная» система - в раздел памяти CPU3 мы можем «смонтировать» любой из доступных кусков ОЗУ 128К. Для удобства они называются «банками». Для ОЗУ 128К это 8 банков по 16КБ, условно нумеруемые от 0 до 7. Итак, в CPU3 можно «смонтировать» любой банк памяти от 0 до 7. Что же остальные разделы? Про CPU0 мы уже говорили - это раздел для ПЗУ, он нам не нужен. Для разделов CPU1 и CPU2 жёстко используются конкретные банки памяти - 5 и 2. Таков стандарт на 128К ZX-Spectrum. Теперь распределение памяти приобретает следующий вид:

64КБ ОЗУ уже есть, надо добавить в Спектрум ещё столько же. Самое очевидное, что можно сделать - это взять ещё 8 микросхем КР565РУ5 и организовать их в виде ещё одной «линейки» ОЗУ, тем более что почти все выводы микросхем будут соединяться параллельно (за исключением сигнала CAS, это 15-й вывод микросхем КР565РУ5), и каком-то образом управлять двумя «линейками» ОЗУ. Просто напаиваем на уже установленные в плату микросхемы КР565РУ5 ещё один «этаж» микросхем. 15-е выводы не припаются к нижним микросхемам, а для всей верхней «линейки» ОЗУ, соединяются между собой. Это будет сигнал /CAS1. Для удобства будем называть «родные» микросхемы ОЗУ - как «линейка 0», а напаянные поверх их микросхемы ОЗУ как «линейка 1». Естественно, от линейки 0 ОЗУ мы отсоединим приходящий сигнал /CAS. В результате получаем целых три сигнала, которые надо куда-то пристроить - /CAS (тот, что приходил на 0-ю линейку ОЗУ), /CAS0 - сигнал CAS на линейку 0 ОЗУ и /CAS1 - сигнал CAS на напаянную линейку ОЗУ.

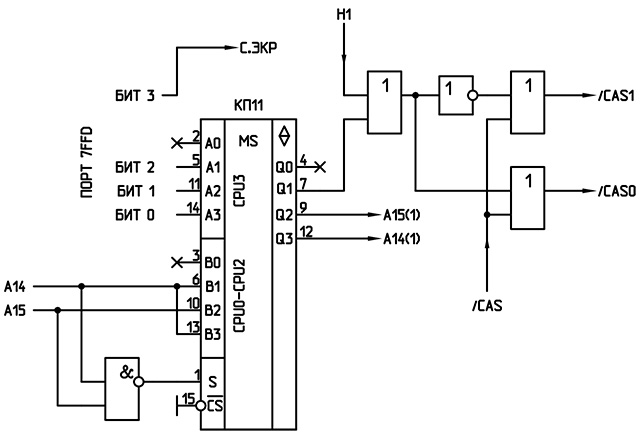

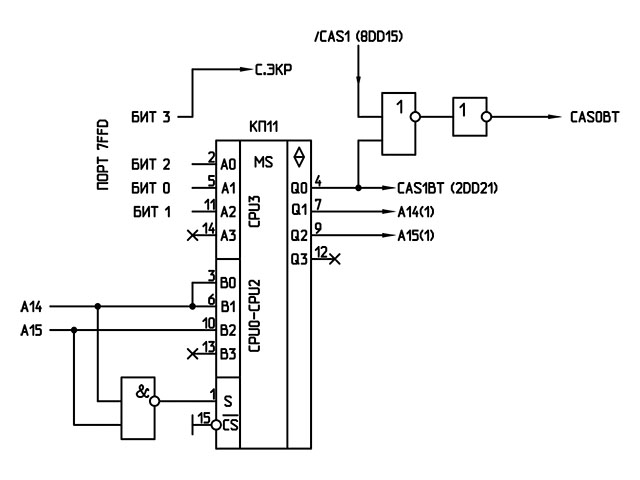

Как я уже говорил, платы расширения ОЗУ Б-1, С-1, ВС-1 сделаны по одному и тому же принципу. Та часть схемы, которая «отвечает» за работу с расширенной памятью выглядит примерно так:

Мы видим, что добавились новые сигналы - А14(1), А15(1) и С.ЭКР. Сигналами А14(1) и А15(1) мы будем заменять сигналы А14 и А15, поступающие на мультиплексоры управления ОЗУ. А сигнал С.ЭКР служит только для быстрого переключения вывода данных на экран. Изначально, когда С.ЭКР=0, вывод на экран идёт из банка 5 ОЗУ. Если С.ЭКР установить в 1, то вывод на экран осуществляется с банка 7 ОЗУ. Речь идёт только про аппаратный вывод данных из ОЗУ на экран. Сам сигнал не переключает никакие банки ОЗУ в памяти!

Порядок обращения к памяти 128К ОЗУ примет следующий вид (для удобства все изменения относительно режима 48К выделены красным цветом):

| /RAS=1 | /RAS=0 | ||||||||||||||||

| MA0 (A0) | MA1 (A1) | MA2 (A2) | MA3 (A3) | MA4 (A4) | MA5 (A5) | MA6 (A6) | MA7 (A7) | MA0 (A8) | MA1 (A9) | MA2 (A10) | MA3 (A11) | MA4 (A12) | MA5 (A13) | MA6 (A14) | MA7 (A15) | ||

| H1=0 | A0 | A1 | A2 | A3 | A4 | A5 | A6 | A7 | A8 | A9 | A10 | A11 | A12 | A13 | A14(1) | A15(1) | |

| H1=1 | H2=0 | H3 | H4 | H5 | H6 | H7 | V3 | V4 | V5 | V0 | V1 | V2 | V6 | V7 | 0 | 1 | С.ЭКР |

| H2=1 | H3 | H4 | H5 | H6 | H7 | V3 | V4 | V5 | V6 | V7 | 0 | 1 | 1 | 0 | 1 | ||

Пройдёмся по логике работы схемы расширения, чтобы понять почему нам нужно было менять A14,15 на адресных мультиплексорах в компьютере.

Все варианты состояния схемы расширения представлены ниже в таблице:

|

/CAS0 линейка 0 ОЗУ |

/CAS1 линейка 1 ОЗУ |

A15(1) | A14(1) | ||

|

CPU0 #0000-#3FFF |

0 | 1 | 0 | 0 |

С адреса #0000 линейки 0 ОЗУ (банк 0) |

|

CPU1 #4000-#7FFF (банк 5) |

1 | 0 | 0 | 1 | С адреса #4000 линейки 1 ОЗУ |

|

CPU2 #8000-#BFFF (банк 2) |

0 | 1 | 1 | 0 | С адреса #8000 линейки 0 ОЗУ |

|

CPU3 #C000-#FFFF |

бит 2 #7FFD | /бит 2 #7FFD | бит 1 #7FFD | бит 0 #7FFD |

Разберём все состояния схемы.

При обращении к областям памяти CPU0-CPU2 работает «нижняя» по схеме часть мультиплексора КП11. Соответственно при обращении к CPU3 включается «верхняя» часть микросхемы.

Скажу сразу, что банки ОЗУ распределены по линейкам ОЗУ следующим образом: банки 0-3 находятся в 0-й линейке ОЗУ, банки 4-7 находятся в 1-й (напаянной) линейке ОЗУ. Такое расположение банков памяти наиболее удобно для работы схемы расширения. И это к вопросу о том, как при работе теста ОЗУ 128К определить по номеру банка ОЗУ неисправную микросхему.

Обращение к CPU0 (как я уже писал этот вариант работы «отсекается» схемой компьютера, но всё равно имеет смысл рассмотреть и его). При этом A14(1)=A14=0, A15(1)=A15=0, и сигналом A14=0 включаем 0-ю линейку ОЗУ. При этом мы обращаемся к линейке 0 ОЗУ по адресам #0000-#3FFF, то есть попадаем в 0-й банк ОЗУ 128К.

Между прочим, из-за особенности схемы «Ленинград-1» при расширении ОЗУ до 128К при записи в область CPU0, то есть в ПЗУ, на самом деле данные пишутся в соответствующие байты банка 0 ОЗУ (именно по той причине, что раздел CPU0 соответствует 0-му банку ОЗУ), из-за чего могут не работать некоторые игры. И при расширении ОЗУ до 128К (и выше) в схему компьютера надо вносить исправление.

Обращение к CPU1. Это область памяти #4000-#7FFF. При этом A14(1)=A14=1, A15(1)=A15=0. Сигналом A14=1 включаем 1-ю линейку ОЗУ (напаянную), и за счёт сигналов A14=1 и A15=0 обращаемся к адресам #4000-#7FFF в 1-й линейке ОЗУ, то есть к банку 5 ОЗУ.

Обращение к CPU2. Это область памяти #8000-#BFFF. При этом A14(1)=A14=0, A15(1)=A15=1. Сигналом A14=0 включаем 0-ю линейку ОЗУ, и за счёт сигналов A14=0 и A15=1 обращаемся к адресам #8000-#BFFF в 0-й линейке ОЗУ, то есть к банку 2 ОЗУ.

Обращение к CPU3. Это область памяти #C000-#FFFF. В этом случае A14(1)= бит 0 порта #7FFD, A15(1)= бит 1 порта #7FDD, а бит 2 порта #7FFD определяет активную линейку ОЗУ (0-оригинальная, 1-напаянная). Соответственно именно из этого режима видно, что банки 0-3 находятся в 0-й линейке ОЗУ, а банки 4-7 находятся в 1-й линейке ОЗУ. Внутри выбранной линейки ОЗУ номер банка определяется сигналами A15(1) и A14(1). А так как при обращении к CPU3 сигналы процессора равны A14=A15=1, то выбранный банк ОЗУ «монтируется» в область памяти #C000-#FFFF.

Также на схему расширения приходит сигнал H1. Его назначение состоит только в том, чтобы выделить тот момент, когда идёт считывание данных из ОЗУ на экран. При этом принудительно включается линейка ОЗУ №1. Почему так? Потому, что банки ОЗУ 5 и 7, из которых возможен вывод на экран, находятся в этой линейке ОЗУ.

И, напоследок, о сигнале С.ЭКР (бит 3 порта #7FFD). Как я уже писал, этот сигнал всего лишь определяет с какого из двух банков ОЗУ (5 или 7) выводит информацию на экран. Теперь посмотрим как это происходит аппаратно. Если этот сигнал равен 0 (при сбросе компьютера), на адресные мультиплексоры на MA7 для старшего байта адреса при выводе на экран поступает лог.0. Мы же помним, что при выводе на экран аппаратно включается линейка №1 ОЗУ (смотрим абзацем выше). При этом вывод на экран идёт начиная с адреса #4000 в 1-й линейке ОЗУ, то есть с 5-го банка ОЗУ. Если же сигнал С.ЭКР=1, то вывод на экран идёт уже с адреса #C000 (MA6=MA7=1) в 1-й линейке ОЗУ, что соответствует банку ОЗУ под номером 7.

ZX-Spectrum с раздельными полями ОЗУ

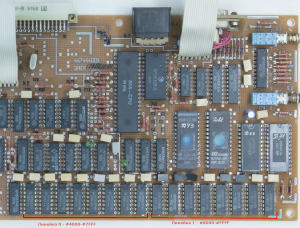

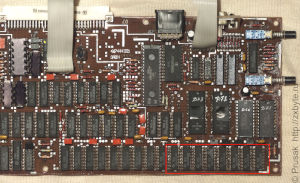

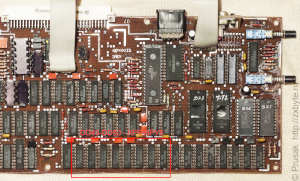

К этому типу компьютеров принадлежит «Байт». Общий принцип построения ОЗУ в таких клонах состоит в наличии двух «линеек» ОЗУ - одна для «медленного» (экранного) ОЗУ, вторая - для остального ОЗУ. Конкретно в «Байте» ОЗУ состоит из «линейки» КР565РУ6 (16КБ ОЗУ по адресам #4000-#7FFF) и одной линейки КР565РУ5 (32КБ ОЗУ по адресам #8000-#FFFF, используется только 32КБ из 64КБ общего объёма всей линейки). Возможны варианты использования линейки ОЗУ на КР565РУ5Д1 или Д2, у которых рабочий объём равен 32КБ.

Для экранного ОЗУ таблица с вариантами доступа имеет следующий вид:

| /RAS0=1 | /RAS0=0 | ||||||||||||||

| VA0 (A0) | VA1 (A1) | VA2 (A2) | VA3 (A3) | VA4 (A4) | VA5 (A5) | VA6 (A6) | VA0 (A7) | VA1 (A8) | VA2 (A9) | VA3 (A10) | VA4 (A11) | VA5 (A12) | VA6 (A13) | ||

|

20=0

данные |

A0 | A1 | A2 | A3 | A4 | A5 | A6 | A7 | A8 | A9 | A10 | A11 | A12 | A13 | |

| 20=1 |

24=0

атрибуты |

3 | 6 | 7 | 8 | 9 | 14 | 15 | 16 | 17 | 18 | 0 | 1 | 1 | 0 |

|

24=1

пиксели |

3 | 6 | 7 | 8 | 9 | 14 | 15 | 16 | 11 | 12 | 13 | 17 | 18 | 0 | |

При сигнале 20 в лог.0 ОЗУ работает в режиме доступа по адресу на шине данных процессора. Адресуются 16КБ (сигналы A0-A13).

При сигнале 20 в лог.1 происходит вывод информации на экран. Вывод информации разделён на вывод пикселей (при сигнале 24 в лог.1) или атрибутов (при сигнале 24 в лог.0).

Доступ к линейке экранного ОЗУ осуществляется сигналом /CAS0, который вырабатывается только при обращении к области памяти CPU1 (A15=0, A14=1, /MREQ=0, /RD или /WR в лог.0).

Для остальной области ОЗУ (линейка на КР565РУ5) таблица с вариантами обращения более проста:

| 90=1 | 90=0 | |||||||||||||||

| MA0 (A0) | MA1 (A1) | MA2 (A2) | MA3 (A3) | MA4 (A4) | MA5 (A5) | MA6 (A6) | MA7 (A7) | MA0 (A8) | MA1 (A9) | MA2 (A10) | MA3 (A11) | MA4 (A12) | MA5 (A13) | MA6 (A14) | MA7 (A15) | |

| K1-K2 | A0 | A1 | A2 | A3 | A4 | A5 | A6 | 0 | A7 | A8 | A9 | A10 | A11 | A12 | A13 | A14 |

| K1-K3 | A0 | A1 | A2 | A3 | A4 | A5 | A6 | 1 | A7 | A8 | A9 | A10 | A11 | A12 | A13 | A14 |

Сигнал 90 активен в лог.0 при чтении или записи в ОЗУ по адресам #8000-#FFFF (A15=0, /MREQ=0, /RD или /WR в лог.0). Логика работы фиксации адреса такова: пока нет обращения к адресному пространству CPU2,CPU3, на ОЗУ выводятся сигналы A0-A6 шины данных, которые осуществляют регенерацию содержимого ОЗУ (процессор Z80 способен делать регенерацию 16КБ ОЗУ, перебирая сигналы A0-A6 на шине адреса). Как только появляется обращение к CPU2,CPU3, сигнал 90 переходит в лог.0, при этом в ОЗУ фиксируется адрес (A0-A14) и по сигналу /CAS1 выдаётся на шину данных.

Как видно, из таблицы, сигнал MA7 не используется (он постоянно либо в лог.0 либо в лог.1 в зависимости от положения перемычки K1-K2-K3), из-за чего работает только «половинка» ОЗУ (32КБ). Это сделано для того, чтобы вместо КР565РУ5 можно было использовать «отбраковки» КР565РУ5Д1(Д2), в которых рабочей является только одна половинка. А положение нужной рабочей «половинки» указывается перемычкой K1-K2-K3.

Соответственно в случае, когда линейка ОЗУ сделана на «нормальных» КР565РУ5, положение перемычки K1-K2-K3 не играет никакой роли. ОЗУ будет нормально работать в любом из положений перемычки (K1-K2 либо K1-K3).

Расширение ОЗУ до 128К

Общая схема расширения ОЗУ до 128К выглядит следующим образом:

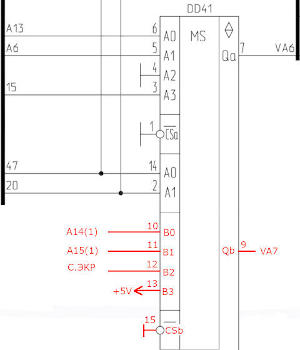

Кроме этого в компьютере «Байт» требуются доработки схемы. Во-первых мы меняем линейку видео-ОЗУ КР565РУ6 на РУ5, у которых добавляется ещё один адресный вывод A7. И чтобы его задействовать используется свободная «половинка» мультиплексора DD41:

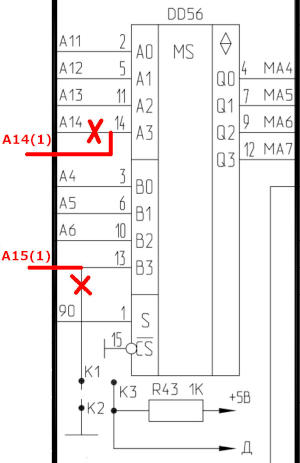

Для подмены A14 и A15 (на A14(1) и A15(1)) на мультиплексоре DD56 надо освободить 2 вывода:

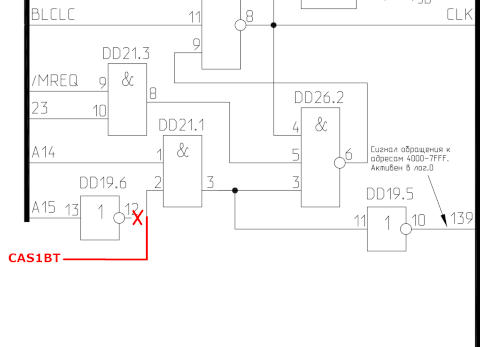

И, наконец, чтобы обеспечить выбор линейки видео-ОЗУ не только в момент обращения к экрану, исправляется узел выбора адресного пространства видео-ОЗУ:

Для экранного ОЗУ таблица с вариантами доступа меняется на:

| /RAS0=1 | /RAS0=0 | ||||||||||||||||

| VA0 (A0) | VA1 (A1) | VA2 (A2) | VA3 (A3) | VA4 (A4) | VA5 (A5) | VA6 (A6) | VA7 (A7) | VA0 (A8) | VA1 (A9) | VA2 (A10) | VA3 (A11) | VA4 (A12) | VA5 (A13) | VA6 (A14) | VA7 (A15) | ||

|

20=0

данные |

A0 | A1 | A2 | A3 | A4 | A5 | A6 | A14(1) | A7 | A8 | A9 | A10 | A11 | A12 | A13 | A15(1) | |

| 20=1 |

24=0

атрибуты |

3 | 6 | 7 | 8 | 9 | 14 | 15 | 1 | 16 | 17 | 18 | 0 | 1 | 1 | 0 | С.ЭКР |

|

24=1

пиксели |

3 | 6 | 7 | 8 | 9 | 14 | 15 | 16 | 11 | 12 | 13 | 17 | 18 | 0 | |||

Для остальной области ОЗУ (линейка на КР565РУ5) таблица с вариантами обращения ещё более упрощается и больше не зависит от положения перемычки К1-К2-К3:

| 90=1 | 90=0 | ||||||||||||||

| MA0 (A0) | MA1 (A1) | MA2 (A2) | MA3 (A3) | MA4 (A4) | MA5 (A5) | MA6 (A6) | MA7 (A7) | MA0 (A8) | MA1 (A9) | MA2 (A10) | MA3 (A11) | MA4 (A12) | MA5 (A13) | MA6 (A14) | MA7 (A15) |

| A0 | A1 | A2 | A3 | A4 | A5 | A6 | A15(1) | A7 | A8 | A9 | A10 | A11 | A12 | A13 | A14(1) |

Как видно, в каждой линейке ОЗУ можно адресовать напрямую с процессора один банк памяти (через A0-13), а управлять банками памяти можно двумя дополнительными сигналами, формируемыми платой расширения. Итого каждая линейка ОЗУ содержит 4 банка памяти. Вместе в двух линейках - 8 банков по 16К, то есть 128КБ.

Разберём, как работает эта схема расширения ОЗУ. Напомню, что линейка ОЗУ, где были РУ6, у нас называется "0-я линейка", а линейка ОЗУ с РУ5 - "1-я линейка". Схема расширения ОЗУ в зависимости от адресуемой области памяти может быть в следующих состояниях:

|

Адресное пространство процессора |

Сигналы, формируемые платой расширения | Пояснения | |||

| A14(1) | A15(1) | CAS1BT | CAS0BT | ||

|

CPU0 (A15=0,A14=0) |

Повторяет A14 (т.е. 0) |

Повторяет A15 (т.е. 0) |

Повторяет A14 (т.е. 0) |

Повторяет /CAS1 (для CPU0 будет равен 1) |

Выбирает банк 0 в линейке 1, т.е. RAM0. В действительности при обращении к этой области памяти выбирается ПЗУ. |

|

CPU1 (A15=0,A14=1) |

Повторяет A14 (т.е. 1) |

Повторяет A15 (т.е. 0) |

Повторяет A14 (т.е. 1) |

1 | Выбирает банк 1 в линейке 0, т.е. RAM5 |

|

CPU2 (A15=1,A14=0) |

Повторяет A14 (т.е. 0) |

Повторяет A15 (т.е. 1) |

Повторяет A14 (т.е. 0) |

Повторяет /CAS1 (для CPU2 будет равен 0) |

|

|

CPU3 (A15=1,A14=1) |

Бит 0 #7FFD | Бит 1 #7FFD | Бит 2 #7FFD |

Если бит 2 #7FFD = 0, CAS0BT повторяет сигнал /CAS1, который для CPU3 равен 0;

Если бит 2 #7FFD = 1, CAS0BT=1 |

|

Теперь более подробно.

Обращение к области памяти CPU1 (#4000-#7FFF, A15=0, A14=1).

При этом A14(1)=A14=1, A15(1)=A15=0, CAS1BT=A14=1, CAS0BT=1. Сигнал CAS0BT=1 запрещает выбор 1-й линейки ОЗУ. Сигналы CAS1BT=1 и A14=1 разрешают выбор линейки 0 ОЗУ. Одновременно сигналами A14(1)=1 и A15(1)=0 в 0-й линейке ОЗУ выбирается 1-й банк памяти, то есть RAM5.

Обращение к области памяти CPU2 (#8000-#BFFF, A15=1, A14=0).

При этом A14(1)=A14=0, A15(1)=A15=1, CAS1BT=A14=0, CAS0BT=1. Сигнал CAS0BT повторяет сигнал /CAS1, который при обращении к CPU2 принимает значение 0, разрешая выбор линейки ОЗУ №1. Одновременно сигналами A14(1)=0 и A15(1)=1 в 1-й линейке ОЗУ выбирается 2-й банк памяти, то есть RAM2.

Обращение к области памяти CPU3 (#C000-#FFFF, A15=1, A14=1).

При этом A14(1)=бит 0 #7FFD, A15(1)=бит 1 #7FFD, CAS1BT=бит 2 #7FFD. А состояние CAS0BT зависит от значения бита 2 порта #7FFD. Если там лог.0, то CAS0BT повторяет состояние сигнала /CAS1, который при обращении к CPU3 равен 0, выбирая линейку 1 ОЗУ. Если же бит 2 #7FFD равен 1, то CAS0BT=1, запрещая выбор линейки 1 ОЗУ, но при этом CAS1BT=1 вместе с A14=1 разрешает выбор 0-й линейки ОЗУ.

Таким образом, битом 2 порта #7FFD переключаются линейки ОЗУ.

Банки ОЗУ 0-3 находятся в 1-й линейке ОЗУ DD51-DD60:

Банки ОЗУ 4-7 находятся в 0-й линейке ОЗУ DD43-DD50:

Если у нас выбрана 0-я линейка ОЗУ (бит 2 порта #7FFD равен 1), банки ОЗУ внутри линейки переключаются сигналами A14(1) и A15(1), которые повторяют значения битов 0 и 1 порта #7FFD. Таким образом получаем доступ к банкам ОЗУ RAM4-RAM7.

Если у нас выбрана 1-я линейка ОЗУ (бит 2 порта #7FFD равено 0), банки ОЗУ внутри линейки переключаются теми же сигналами A14(1) и A15(1), обеспечивая выбор банков ОЗУ RAM0-RAM3.

Напоследок немного о сигнале С.ЭКР. Он служит только для быстрого переключения вывода данных на экран. Изначально, когда С.ЭКР=0, вывод на экран идёт из банка 5 ОЗУ (смотрим на таблицу состояний линейки 0 ОЗУ, VA7=1, VA15=0). Если С.ЭКР установить в 1, то вывод на экран осуществляется с банка 7 ОЗУ (VA15=1, VA7=1). Речь идёт только про аппаратный вывод данных из ОЗУ на экран. Сам сигнал не переключает никакие банки ОЗУ в памяти!